# جلسة العملي الثالثة (المخبر B7) برمجة الـ FPGA باستخدام اللغة VHDL

#### 1 تهيئة بيئة العمل:

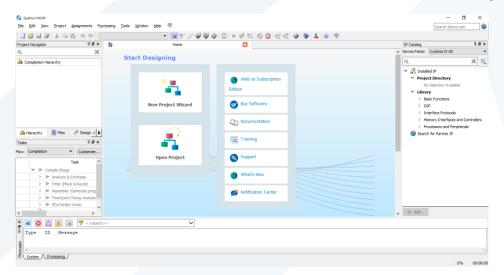

بعد توصيل لوحة الـ FPGA مع الكمبيوتر عن طريق منفذ الـ USB نقوم بتشغيل برنامج الـ FPGA مع الكمبيوتر عن طريق منفذ الـ فنحصل على النافذة التالية:

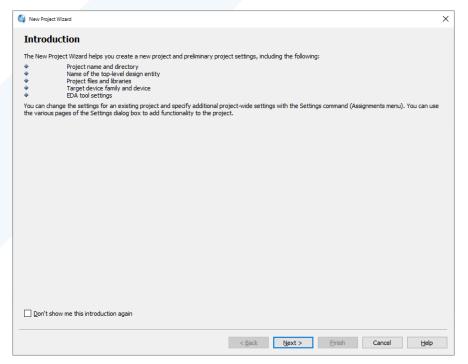

في البداية سنقوم بإنشاء مشروع جديد عن طريق قائمة New Project Wizard حيث تظهر لنا النافذة التالية:

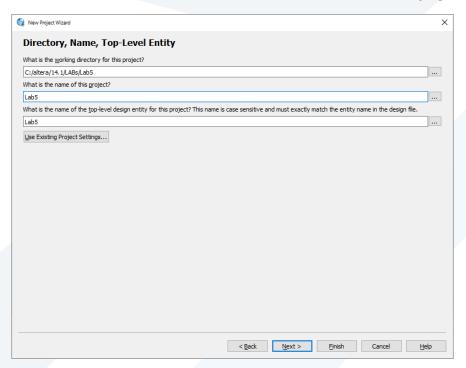

بالضغط على Next نحصل على النافذة التالية والتي من خلالها نقوم بإدخال موقع تخزين المشروع الجديد واسمه ليتم بعدها الضغط على الزر Next

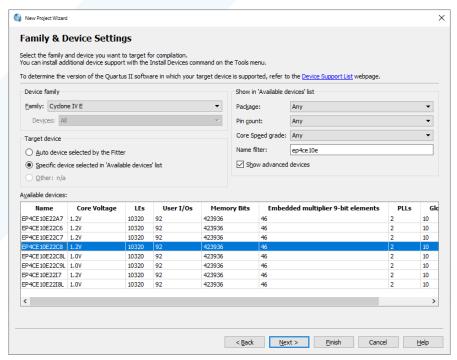

بعد ذلك ستظهر لدينا نافذة جديدة لتحديد نوع المشروع هل هو فارغ أم نسخة مخزنة مسبقاً Template سنختار هنا انشاء مشروع فارغ ومن ثم نضغط على زر Next لتظهر لدينا نافذة جديدة مهمتها إضافة ملفات جاهزة إلى هذا المشروع. هنا سنتابع دون إضافة أي ملف عن طريق الضغط على الزر Next لنحصل على نافذة جديدة كما هو موضح بالشكل والتي من خلالها نقوم بتحديد نوع الـ FPGA الخاص بالتجربة وهو هنا EP4CE10E22C8

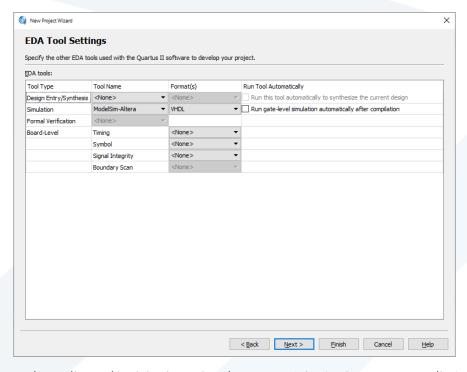

بعد ذلك تظهر لدينا نافذة اعدادات الـ EDA كما هو مبين بالشكل:

عند الضغط على الزر Next سنحصل على نافذة جديدة تظهر ملخص اعدادات المشروع الجديد ليتم بعدها الضغط على زر Finish

## 2 <u>تصميم الدارات باستخدام كود VHDL</u>

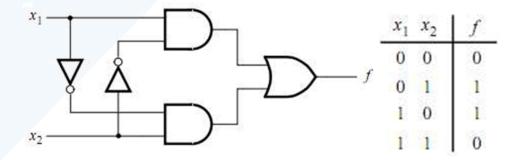

كمثال على التصميم، سوف نستخدم دائرة التحكم في الضوء ثنائية الاتجاه الموضحة في الشكل، والتي تقوم بالتحكم في ضوء واحد من أي من المفتاحين x1 و x2، حيث يقابل المفتاح المغلق القيمة المنطقية 1

جدول الحقيقة للدارة كما هو موضح في الشكل. لاحظ أن هذه مجرد وظيفة Exclusive-OR للمدخلات x1 و x2 ، لكننا سنحددها باستخدام البوابات الموضحة.

#### 1.2 انشاء ملف التصميم

في البداية سنقوم بكتابة الكود البرمجي للدارة السابقة وسنستخدم لذلك محرر النصوص الخاص بـ Quartus II عن طريق → New → New ونختار VHDL File من القائمة ثم نضغط على الزر OK. سيظهر لدينا محرر النصوص والذي ضمنه نقوم بكتابة الكود البرمجي الخاص بالدارة وهو على الشكل التالي:

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY Lab5 IS

PORT ( x1, x2 : IN STD_LOGIC;

f: OUT STD_LOGIC);

END Lab5;

ARCHITECTURE LogicFunction OF Lab5 IS

BEGIN

f <= (x1 AND NOT x2) OR (NOT x1 AND x2);

END LogicFunction;

```

الآن نقوم بحفظ ملف الـ VHDL وليكن باسم light.vhd وذلك عن طريق Save As مع اختيار الخيار VHDL وليكن باسم Save الآن نقوم بحفظ على الزر project

يمكن إضافة ملف الـ VHDL إلى المشروع عن طريق Add/Remove Files in Project  $\rightarrow$  Add/Remove Files مريق Assignments  $\rightarrow$  Settings ومن ثم الضغط على الخيار Files

### 2.2 ترجمة الدارة (Compile):

يتم ذلك عن طريق Processing → Start Compilation أو عن طريق الضغط على الزر 🚺 من قائمة الأدوات

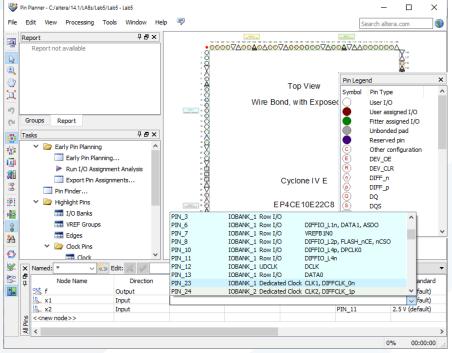

#### 3.2 اسناد المنافذ Pin Assignment:

يتم ذلك عم طريق Assignments → Pins Planer وربط كل منفذ سواء المداخل أو المخارج إلى المنفذ المناسب ضمن لوحة الـ FPGA كما هو موضح بالشكل

تمتلك لوحة الـ FPGA مجموعة من الوحدات المحيطية مثل المفاتيح (Switches) والليدات (LEDs) و CEDs) و 7-Segments بالإضافة إلى LCD والتي ترتبط مع منافذ PIN كما هو موضح:

| Switch | FPGA pin |    | LED |

|--------|----------|----|-----|

| SW7    | 120      | 84 | D7  |

| SW6    | 119      | 83 | D6  |

| SW5    | 115      | 80 | D5  |

| SW4    | 114      | 77 | D4  |

| SW3    | 113      | 76 | D3  |

| SW2    | 112      | 75 | D2  |

| SW1    | 111      | 74 | D1  |

| SW0    | 110      | 73 | D0  |

| Anode for char. | J6 pin | FPGA pin | segment | J7 pin | FPGA pin |

|-----------------|--------|----------|---------|--------|----------|

| 0               | 1      | 25       | а       | 1      | 15       |

| 1               | 2      | 27       | b       | 2      | 16       |

| 2               | 3      | 28       | С       | 3      | 17       |

| 3               | 4      | 29       | d       | 4      | 18       |

|                 |        |          | е       | 5      | 20       |

|                 |        |          | f       | 6      | 21       |

|                 |        |          | g       | 7      | 22       |

|                 |        |          | dp      | 8      | 24       |

#### 4.2 اعداد وبرمجة لوحة الـ FPGA:

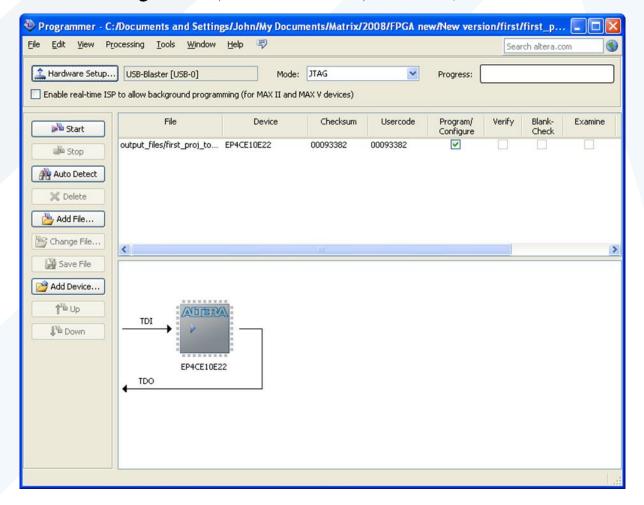

في البداية يجب وضع مفتاح الـ RUN/PROG ضمن لوحة الـ FPGA على وضعية الـ RUN ومن ثم فتح نافذة الـ → RUN/PROG لتظهر لدينا النافذة الموضحة بالشكل والتي تستخدم لإعداد وتحميل البرنامج على لوحة الـ FPGA. هنا يتم اختيار الهاردوير كـ USB-Blaster عن طريق الضغط على الزر Hardware Setup. كما وسيتم إضافة الملف الذي تم ترجمته والموجود ضمن المجلد output. بعد ذلك يتم الضغط على الزر Start ليتم تحميل البرنامج على لوحة الـ FPGA

## 3 <u>تمرين1:</u>

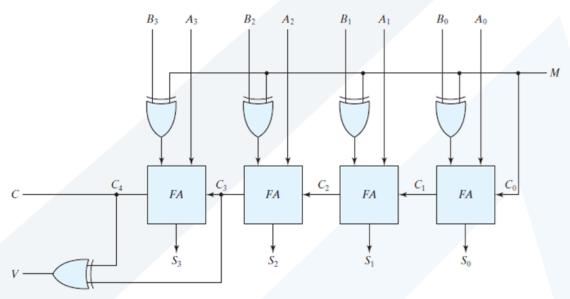

المطلوب برمجة دارة جامع وطارح ثنائي ذو دخل بحجم 4 بت باستخدام برنامج الـ Quartus II ولغة الـ VHDL وتنفيذه على لوحة الـ FPGA ومقارنة النتائج مع جدول الحقيقة الخاص بالدارة

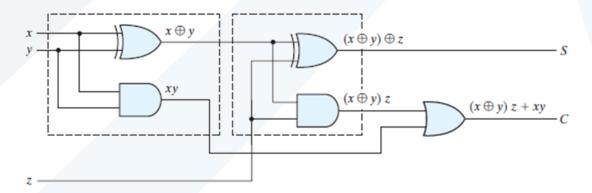

علماً أن دارة الجامع الكامل تعطى بالشكل التالي: