### تصميم رقمي متقدم Advanced Digital Design

Dr.-Eng. Samer Sulaiman 2021-2022

- أساسيات التصميم الرقمي

- عناصروتقنيات التصميم الرقمي التو افقي والتعاقبي (المتسلسل)

- نمذجة التصميم الرقمي باستعمال لغة توصيف الكيان الصلب VHDL

- المحاكاة الوظيفية والزمنية للأنظمة الرقمية

- اساسيات البرمجة بلغة الـVHDL:

- طریقة کتابة شیفرة (کود) الـVHDL:

- في لغة VHDL إذا وضع (--) قبل سطر التعليمة فهذا يدل على أن السطر هو تعليقات أو ملاحظات.

- يجب أن تنتهي جميع أسطر التعليمات والتصريحات بفاصلة منقوطة (;)

- عند التصريح عن أكثر من متحول تستخدم الفاصلة للفصل بينهم (,)

- إسناد قيمة ما إلى إشارة رمزها(=>)، بينما إسناد قيمة ما إلى متحول والتصريح عن قيمة ثابتة ولتعيين قيمة ابتدائية

- رمزها (=:)

- يمكن استخدام الأرقام و الحروف و(\_) للتصريح عن

أسماء المتحولات و الإشارات

- لا يمكن أن يبدأ الاسم برقم ، وكذلك لا يمكن استخدام كلمة محجوزة في الاسم .

- لغة VHDL غير حساسة لحالة الحروف (صغيرة أو كبيرة)

- خلافاً لبرامج الحاسوب العادية التي تكون متسلسلة التنفيذ

فإن لغة الـVHDL تنفذ التعليمات على التفرع لذلك نقول

VHDL code بدلا من VHDL code

- العمليات الأساسية المتوفرة في لغة VHDL

|                    | Operator Class | Operator                      |  |

|--------------------|----------------|-------------------------------|--|

| Highest precedence | Miscellaneous  | **, ABS, NOT                  |  |

|                    | Multiplying    | *, /, MOD, REM                |  |

|                    | Sign           | +, -                          |  |

|                    | Adding         | +, -, &                       |  |

|                    | Shift          | SLL, SRL, SLA, SRA, ROL, ROR  |  |

|                    | Relational     | =, /=, <, <=, >, >=           |  |

| Lowest precedence  | Logical        | AND, OR, NAND, NOR, XOR, XNOR |  |

- اساسيات البرمجة بلغة الـVHDL:

- طريقة كتابة شيفرة (كود) الـVHDL:

- التصريح عن الإشارات ضمن لغة الـVHDL:

- · الإشارات عبارة عن المتحولات الداخلية التي تستخدم لإيصال خرج إحد المكونات الداخلية إلى دخل مكون داخلي أخر

- يتم ذلك كما يلي:

- SIGNAL a: STD\_LOGIC;

SIGNAL b: STD\_LOGIC\_VECTOR(7 DOWNTO 0);

- أمثلة عن التصريح عن إشارات مختلفة:

- SIGNAL a: STD\_LOGIC; SIGNAL b: STD\_LOGIC\_VECTOR(3 DOWNTO 0); SIGNAL c: STD\_LOGIC\_VECTOR(3 DOWNTO 0); SIGNAL d: STD\_LOGIC\_VECTOR(15 DOWNTO 0); SIGNAL e: STD\_LOGIC\_VECTOR(8 DOWNTO 0); a <= '1'; b <= "0000"; -- Binary base assumed by default c <= B"0000"; -- Binary base explicitly specified d <= X"AF67"; -- Hexadecimal base e <= O"723"; -- Octal base</li>

- اساسيات البرمجة بلغة الـVHDL:

- طريقة كتابة شيفرة (كود) الـVHDL:

- التصريح عن الإشارات ضمن لغة الـVHDL:

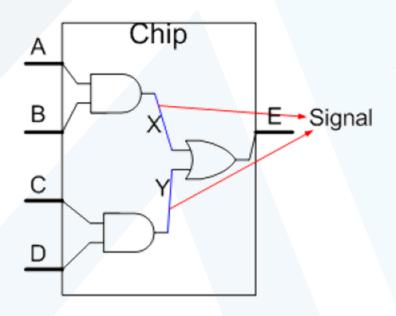

- مثال أكتب شيفرة الـVHDL للدارة المنطقية التالية:

- اساسيات البرمجة بلغة الـVHDL:

- طریقة کتابة شیفرة (کود) الـVHDL:

- التصريح عن الإشارات ضمن لغة الـVHDL:

- مثال أكتب شيفرة الـVHDL للدارة المنطقية التالية:

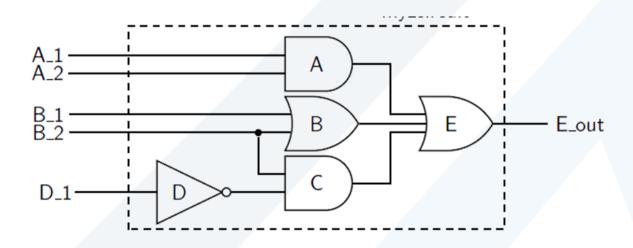

- اساسيات البرمجة بلغة الـVHDL:

- طريقة كتابة شيفرة (كود) الـVHDL:

- التصريح عن الإشارات ضمن لغة الـVHDL:

- · مثال أكتب شيفرة الـVHDL للدارة المنطقية التالية:

```

entity my circuit is

port (

A_1,A_2,B_1,B_2,D_1: in std_logic;

E out:out std logic);

end my circuit;

architecture my_circuit_arc of my_circuit is

signal A_out, B_out, C_out : std_logic;

begin

A out \leq A 1 and A 2;

يمكن كتابتها ايضاً بالشكل التالى بدون الحاجة

B out <= B 1 or B 2;

إلى التصريح عن الاشارات:

C_{out} \leftarrow (not D_1)  and B_2;

E_{out} \le (A_1 \text{ and } A_2) \text{ or } (B_1 \text{ or } B_2)

E_out <= A_out or B_out or C_out;</pre>

end my circuit arc;

or ((not D_1) and B_2);

```

- اساسيات البرمجة بلغة الـVHDL:

- طریقة کتابة شیفرة (کود) الـVHDL:

- مثال: أكتب شيفرة الـVHDL لدارة جامع كامل بخانة واحدة

- المرحلة الأولى:

- توصيف النظام على أنه صندوق أسود يمتلك عدد ا من المداخل والمخارج بمواصفات محددة.

- إن الدارة الرقمية للجامع الكامل عبارة عن دارة ذات ثلاثة مداخل ومخرجين:

- دخل أول: A، دخل ثانى: B، دخل ثالث: الحمل. Cin.

- خرج أول: يمثل المجموع A + B = Sum خرج ثاني: يمثل الحمل الناتج. Cout

- جدول الحقيقة للجامع الكامل:

- المرحلة الثانية:

- توصيف النظام من الداخل من خال توصيف العلاقة التي تربط المداخل بالمخارج اعتماداً على العلاقات المنطقية المستنتجة من جدول الحقيقة

|   |   |     |     | *    |

|---|---|-----|-----|------|

| A | В | Cin | Sum | Cout |

| 0 | 0 | 0   | 0   | 0    |

| 0 | 0 | 1   | 1   | 0    |

| 0 | 1 | 0   | 1   | 0    |

| 0 | 1 | 1   | 0   | 1    |

| 1 | 0 | 0   | 1   | 0    |

| 1 | 0 | 1   | 0   | 1    |

| 1 | 1 | 0   | 0   | 1    |

| 1 | 1 | 1   | 1   | 1    |

- اساسيات البرمجة بلغة الـVHDL:

- طريقة كتابة شيفرة (كود) الـVHDL:

- مثال: أكتب شيفرة الـVHDL لدارة جامع كامل بخانة واحدة

- المرحلة الثانية:

- الشيفرة المطلوبة:

```

LIBRARY ieee:

USE ieee.std_logic_1164.all;

Summation:

ENTITY full adder IS

Sum <= A XOR B XOR Cin;

PORT (A,B,cin: IN STD LOGIC;

Sum, cout : OUT STD_LOGIC );

Sum

END full adder;

ARCHITECTURE dataflow OF full adder IS

Cout

Carry:

Cout <= (A AND B) OR

BEGIN

(A AND Cin) OR

Sum <= A XOR B XOR cin;

(B AND Cin);

cout <= (A AND B) OR (cin AND A) OR (cin AND B);</pre>

END dataflow;

```

- اساسيات البرمجة بلغة الـVHDL:

- طریقة کتابة شیفرة (کود) الـVHDL:

- وظيفة: أكتب شيفرة الـVHDL لدارة جامع كامل بخانة واحدة علماً أن الدارة المنطقية المكافئة له موضحة بالشكل التالي:

- طريقة التنفيذ في اللغة VHDL:

- على خلاف لغات البرمجة التقليدية يتم تنفيذ التعليمات في لغة VHDL على التوازي (Concurrent (parallel

- ويتم تنفيذ الكود البرمجي بنفس الوقت تقريبا لكافة التعليمات

- يمكن القول ان إشارات الدخل تنقل إلى الخرج بزمن مهمل تقريباً باستثناء تأخير الانتشار

- نظراً لهذ الخصوصية في تنفيذ التعليمات ونظراً للحاجة في بعض الحالات من تحويل التنفيذ إلى النمط التقليدي أي ترتيب تنفيذ التعليمات بحسب حاجة المبرمج وما يراه من ضرورة في عمل النظام

- تم إيجاد مجموعة تعليمات كتعليمة End process .. Process التي يمكن إضافتها في وحدة التوصيف الداخلي ليتم تنفيذ التعليمات التي تذكر بعدها بترتيب ورودها من الأعلى إلى الأسفل

- مما يؤدي إلى تحويل آلية التنفيذ إلى النمط التتابعي Sequential

- من أنماط التعليمات التي يتم تنفيذ ا بصورة تسلسلية نذكر PROCESS, FUNCTION, PROCEDURE، حيث يتم تنفيذ ما بداخل هذه الكتل بشكل تسلسلي

- لكن على مستو الكتلة نفسها فإنها تنفذ تفرعيا شانها شأن أي تعليمة في VHDL،

- وبالتالي تكون مهمتها تحقيق الترتيب أو التزامن في تنفيذ التعليمات

- تسمى بـ GUARDED BLOCK، أو محطات الانتظار التي يكون من مهامها الأساسية منع الانتقال إلى كتلة برمجية أخر حتى يتحقق شرط ما يكون شرط التزامن مثلا

- تعليمات البنية التفرعية في اللغة VHDL:

- عمليات الإسناد (=>)

- العمليات المنطقية.

- العمليات الحسابية.

- تعلیمة when-else بأشكالها (with-select-when و when-else)

- تعليمة Generate

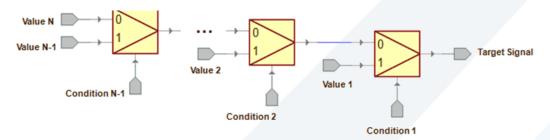

- ' تعليمة when:

- تأخذ عدة أشكال:

- الشكل الأول When Else:

target\_signal <= value1 when condition1 else

value2 when condition2 else

... valueN-1 when conditionN-1 else

valueN;</li>

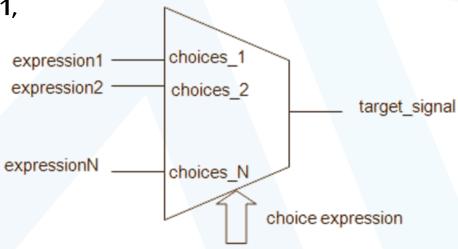

- تعليمات البنية التفرعية في اللغة VHDL:

- تعليمة when:

- تأخذ عدة أشكال:

- الشكل الثاني With –Select-When:

with choice\_expression select target\_signal <= expression1 when choices\_1, expression2 when choices\_2, ... expressionN when choices\_N;

- تعليمات البنية التفرعية في اللغة VHDL:

- تعليمة when:

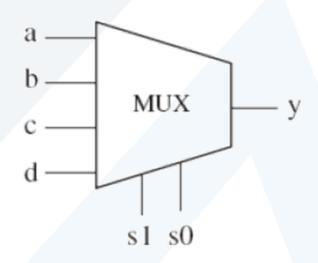

- مثال: أكتب شيفرة الـVHDL لدارة الناخب المبينة في الشكل:

- LIBRARY ieee;

USE ieee.std\_logic\_1164.all;

ENTITY example IS

PORT (a, b, c, d, s0, s1: IN STD\_LOGIC;

y: OUT STD\_LOGIC);

END example;

ARCHITECTURE Mux OF example IS

BEGIN

y <= (a AND NOT s1 AND NOT s0) OR

(b AND NOT s1 AND s0) OR

(c AND s1 AND NOT s0) OR

(d AND s1 AND s0);

END Mux;</li>

| input | output |  |  |

|-------|--------|--|--|

| s     | x      |  |  |

| 0.0   | a      |  |  |

| 0.1   | b      |  |  |

| 1 0   | С      |  |  |

| 1 1   | d      |  |  |

- تعليمات البنية التفرعية في اللغة VHDL:

- تعليمة when:

- مثال: أكتب شيفرة الـVHDL لدارة الناخب المبينة في الشكل:

- الشكل الأول

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY example IS

PORT (a, b, c, d, s0, s1: IN STD_LOGIC;

y: OUT STD_LOGIC);

END example;

ARCHITECTURE Mux OF example IS

BEGIN

y <= (a AND NOT s1 AND NOT s0) OR

(b AND NOT s1 AND s0) OR

(c AND s1 AND NOT s0) OR

(d AND s1 AND s0);

END Mux;</li>

```

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY mul IS

PORT ( a, b, c, d: IN STD_LOGIC;

s: IN STD_LOGIC_VECTOR (1 DOWNTO 0);

y: OUT STD_LOGIC);

END mul;

ARCHITECTURE mux OF mul IS

BEGIN

y <= a WHEN s="00" ELSE

b WHEN s="01" ELSE

c WHEN s="10" ELSE

d;

END mux;</li>

```

- تعليمات البنية التفرعية في اللغة VHDL:

- تعليمة when:

- مثال: أكتب شيفرة الـ VHDL لدارة الناخب المبينة في الشكل:

- الشكل الثاني

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY example IS

PORT ( a, b, c, d, s0, s1: IN STD_LOGIC;

y: OUT STD_LOGIC);

END example;

ARCHITECTURE Mux OF example IS

BEGIN

y <= (a AND NOT s1 AND NOT s0) OR

(b AND NOT s1 AND s0) OR

(c AND s1 AND NOT s0) OR

(d AND s1 AND s0);

END Mux;</li>

```

LIBRARY ieee; USE ieee.std\_logic\_1164.all; **ENTITY mul IS** PORT (a, b, c, d: IN STD\_LOGIC; s: IN STD\_LOGIC\_VECTOR (1 DOWNTO 0); y: OUT STD\_LOGIC); END mul; ARCHITECTURE mux OF mul IS **BEGIN** WITH s SELECT y <= a WHEN "00", -- notice "," instead of ";" **b WHEN "01"**, c WHEN "10", d WHEN OTHERS; -- cannot be "d WHEN "11" " **END** mux;

- تعليمات البنية التفرعية في اللغة VHDL:

- تعليمة when:

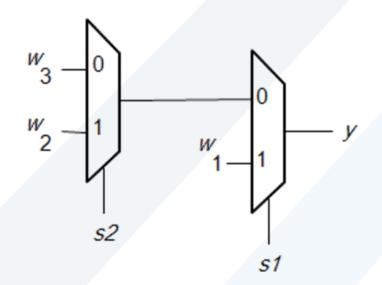

- وظيفة: أكتب شيفرة الـVHDL لتوصيف النظام المبين بالشكل التالي:

- تعليمات البنية التفرعية في اللغة VHDL:

- تعليمة when:

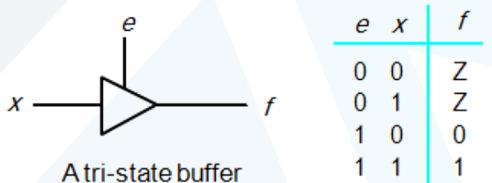

- مثال: أكتب شيفرة الـ VHDL لتوصيف دارة عازل ثلاثي الحالة بمدخل تمكين واحد:

- LIBRARY ieee;

USE ieee.std\_logic\_1164.all;

ENTITY tri\_state IS

PORT (ena: IN STD\_LOGIC;

input: IN STD\_LOGIC;

output: OUT STD\_LOGIC);

END tri\_state;

ARCHITECTURE dataflow OF tri\_state IS

BEGIN

output <= input WHEN (ena = '1') ELSE 'Z';

END dataflow;</li>

- تعليمات البنية التفرعية في اللغة VHDL:

- تعليمة when:

- مثال: المطلوب تصميم دارة عازل لثمانية خانات بمدخلي تمكين متعاكسيين:

- تعليمات البنية التفرعية في اللغة VHDL:

- تعليمة when:

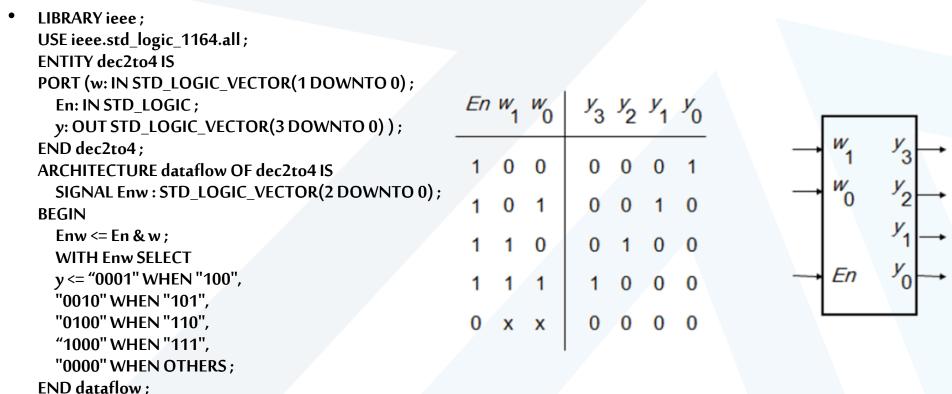

- مثال: أكتب شيفرة الـVHDL لتوصيف دارة المشفر الموضحة بالشكل:

- تعليمات البنية التفرعية في اللغة VHDL:

- تعليمة when:

- مثال: أكتب شيفرة الـ VHDL لتوصيف دارة فاك تشفير الأولوية الموضحة بالشكل:

```

LIBRARY ieee:

USE ieee.std_logic_1164.all;

ENTITY priority IS

PORT (w:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

y:OUT STD_LOGIC_VECTOR(1 DOWNTO 0);

z:OUT STD LOGIC);

END priority;

y<sub>1</sub> y<sub>0</sub>

w_0

ARCHITECTURE dataflow OF priority IS

BEGIN

W1

y \le "11" WHEN w(3) = '1' ELSE

"10" WHEN w(2) = '1' ELSE

"01" WHEN w(1) = '1' ELSE "00";

z \le 0' \text{ WHEN } w = 0000'' \text{ ELSE } 1';

W3

END dataflow

```